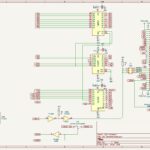

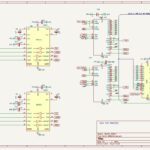

Das KiCAD Projekt ist noch im Aufbau. Es sind noch die Teile für das klasische ECB-Interface und die Variante mit dem Intel 8253 enthalten. Vor dem Layout müssen die nicht benötigten Teile entfernt werden, sonst passt das nicht auf einer Euro-Karte ;-))

Die Hardware ist damit erstmal abgeschlossen.

Softwareseitig gibt es noch einige Baustellen, Module noch weiter aufdröseln damit per Label die bedingte Assemblierung besser genutzt und Vereinheitlicht werden kann. Durch die unterschiedliche Hardware in meiner Sammlung will ich nicht für jeden eine Sonderlocke bauen.

Die Integration der IDE-Karte ist abgeschlossen:

-

- CP/M Boot von der „Platte“

- so stehen 8MB Speicherplatz zur Verfügung

- einfacher BIOS Austausch mit R / S (lesen, schreiben der Systemspuren)

- mit dem Intel-Hexlader kann das BIOs leicht angepasst werden

Das BIOS wurde, wie im CP/M Moppel, mit dem zusätzlichem ITT3030 Format ergänzt. Damit ist auch hier der Datenaustausch mit dem Prof180 gesichert.

Nun kann er erstmal mit der gängigen Software gefüllt werden…

beim füllen der IDE-Karte tauchten erhebliche Probleme auf:

- Viele alte Disketten haben immer wieder fehlende Sektoren, trotz Neuformatierung, also auf dem Prof180 ein paar Disketten nach der Formatierung auch überprüfen lassen.

- Dateien größer als 8kByte können nicht von Diskette auf die CF-Karte kopiert werden

- Schreiben auf Diskette nur bis Track 36 möglich

Das erzeugte bei mir viele Fragezeichen über meinem Kopf, zuerst dachte ich das meine programmierkünste schuld sind – ja da gab es auch ein paar Fehler. Also erstmal alles auf dem CP/M Moppel ausprobieren und testen und testen, schön mit großen und sehr großen Dateien. Hierzu ein kleines Basicprogramm von Fritz geliehen was RECORDS schön durchnummeriert und auf Diskette schreibt. Dabei noch eine CP/M Macke in meinem System aufgefallen, es wollte nicht mehr als 128 Records auf Diskette schreiben, auf der CF-Karte kein Problem. So habe ich die Testdiskette auf dem Prof erstellt, der hat damit kein Problem. Später mit dem P2DOS als BDOS Ersatz war diese Eigenart verschwunden – funktioniert aber nur mit dem NSC800 (Z80). So langsam kam ich zu dem Schluß das es nur an der Hardware liegen konnte.

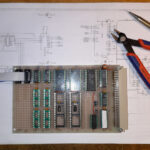

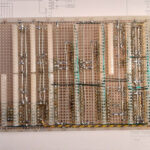

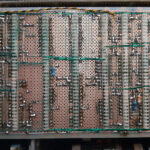

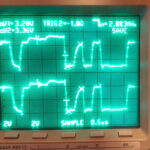

Mit dem Oszi erstmal den BUS betrachtet, sieht nicht wirklich schön aus. Sehr rund und wenig Pegel – könnte an der Stromversorgung liegen. Kleine Verbesserungen standen sowieso noch aus, also komplett zerlegt und dabei die Backplane mit 1,5² eine solidere Stromversorgung versehen. Naja das war nicht die Ursache.

Mit dem Oszi erstmal den BUS betrachtet, sieht nicht wirklich schön aus. Sehr rund und wenig Pegel – könnte an der Stromversorgung liegen. Kleine Verbesserungen standen sowieso noch aus, also komplett zerlegt und dabei die Backplane mit 1,5² eine solidere Stromversorgung versehen. Naja das war nicht die Ursache.

Das Taktsignal auf dem FDC fand ich auch nicht schön, Quarz und 7404 gegen entsprechendem Oszilator getauscht – schon besser.

Erst der Austausch des WD170 gegen einen WD1772 brachte den ersten Erfolg. Nun irrte der Kopf nicht mehr ziellos über die Diskette. Da war dann noch das Problem mit MBASIC, versank immer wieder ins NIRAWANA, Programme wie STAT, DDT oder PIP liefen aber absolut stabil – da kam der „Geistesblitz“ – die sind ja alle viel kleiner, unter 8kByte. Die Speicherkarte hat ein Problem und zwar die untere Hälfte der 2.Karte für BANK1.

Der Adressdecoder 74LS138 hatte ne Macke, vieleicht gefiel ihm der Rucksack nicht ;-). Das ist natürlich der Bereich, der vom Monitor nur mit einigen Tricks zu erreichen ist…

Nun ist es wirklich schön.

Fortsetzung folgt …